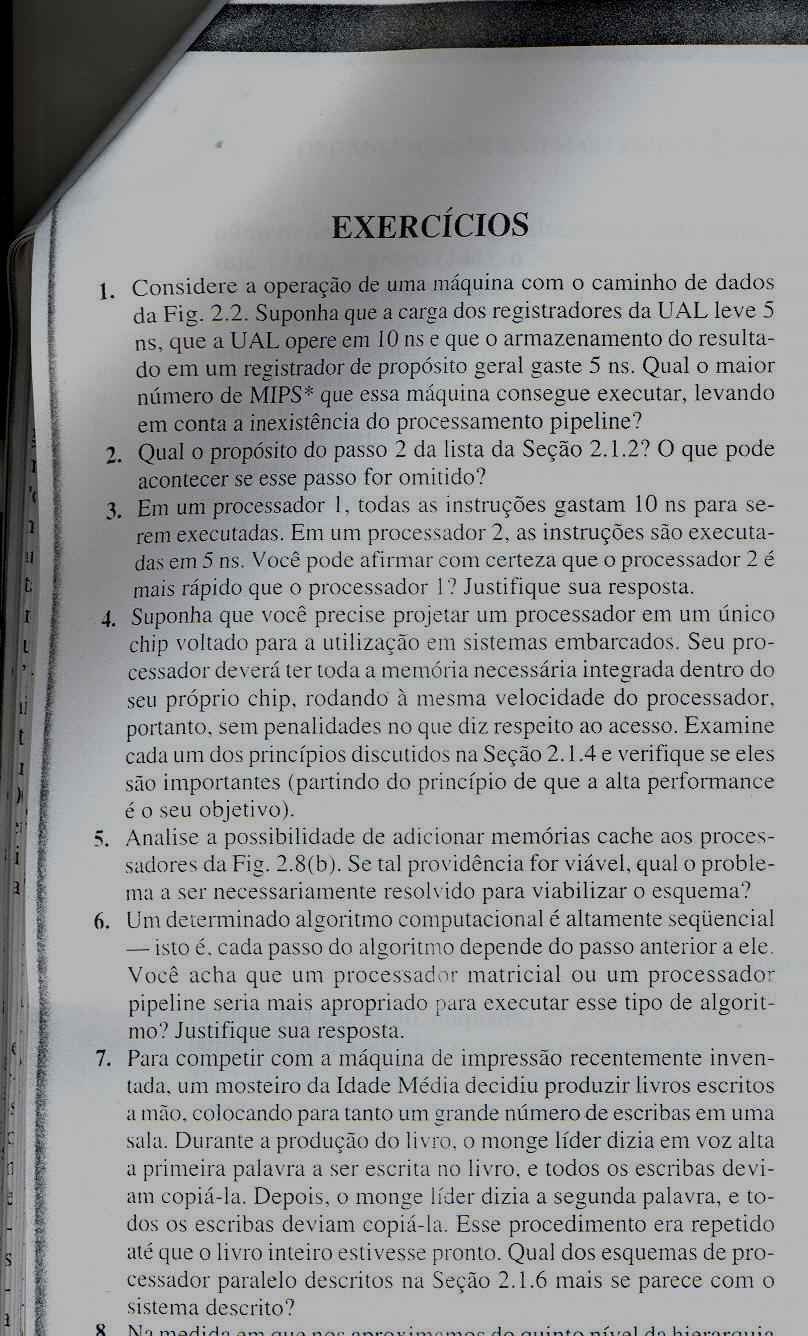

Figura 2.10 Número de bits por célula de

alguns computadores comerciais de interesse

(Obtida do material, disponível na internet, do livro

do Tanenbaum, 2001)

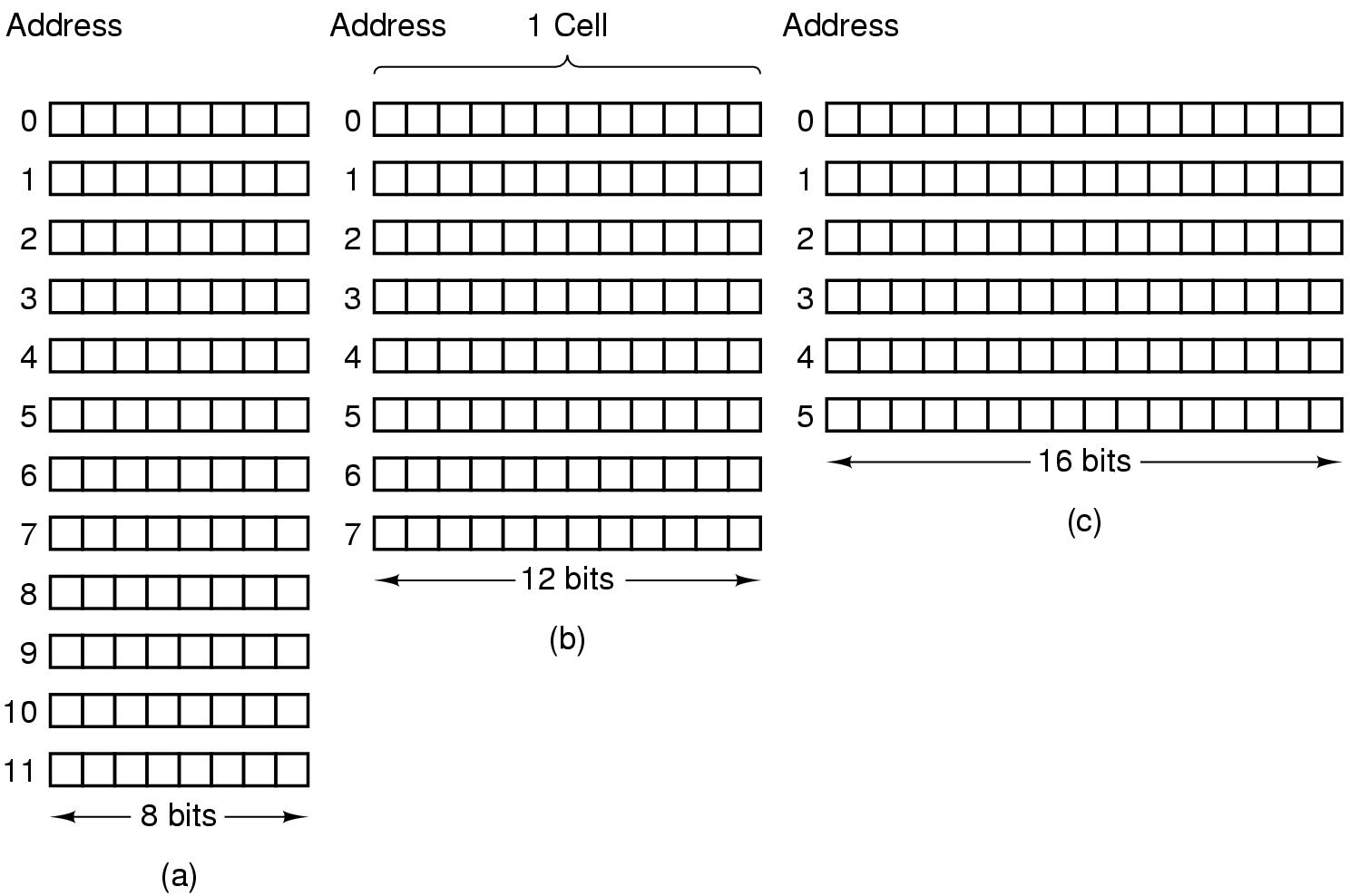

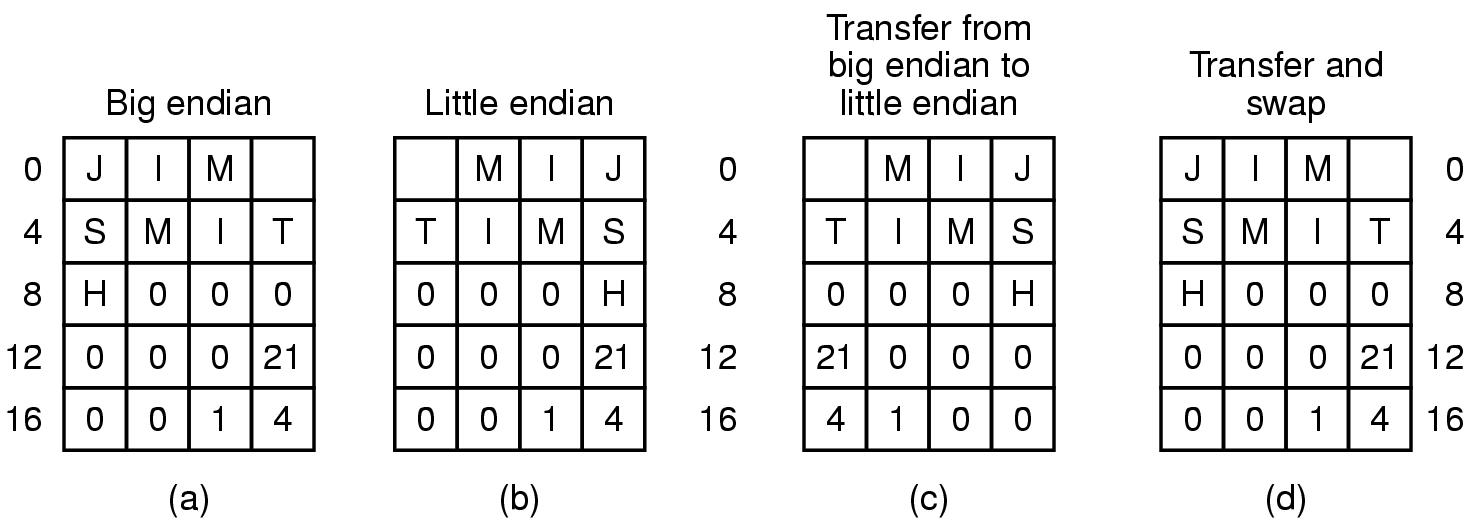

Figura 2.11 (a) Memória big endian. (b) Memória

little endian

(Obtida do material, disponível na internet, do livro

do Tanenbaum, 2001)

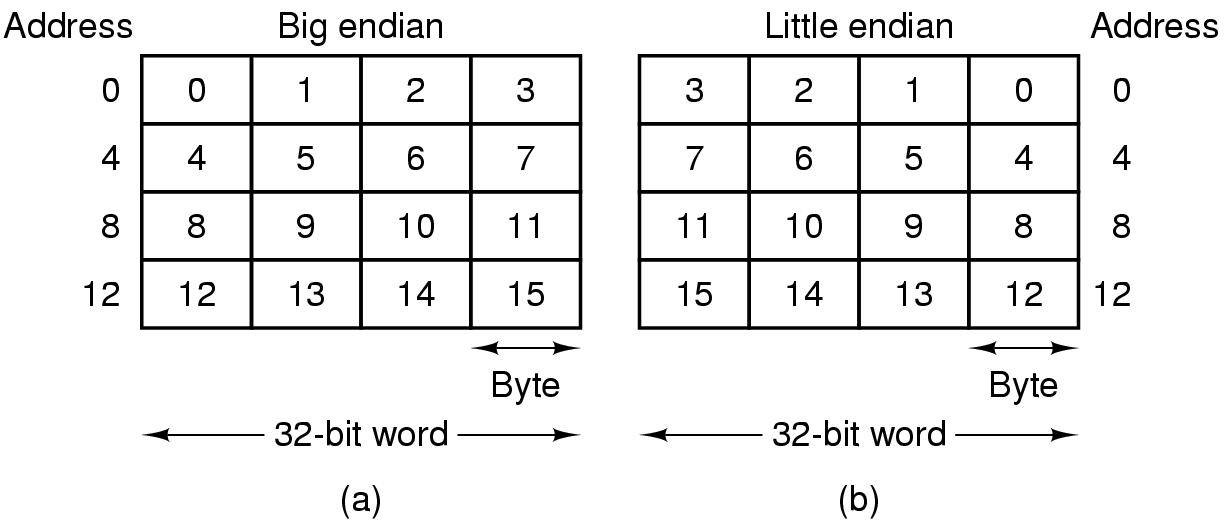

Figura 2.12 (a) Registro de determinado funcionário

em uma máquina big endian. (b) O mesmo registro em uma máquina

little endian. (c) Resultado da transferência do registro da máquina

big endian para a little endian. (d) O resultado da troca de bytes de (c)

(Obtida do material, disponível na internet, do livro

do Tanenbaum, 2001)

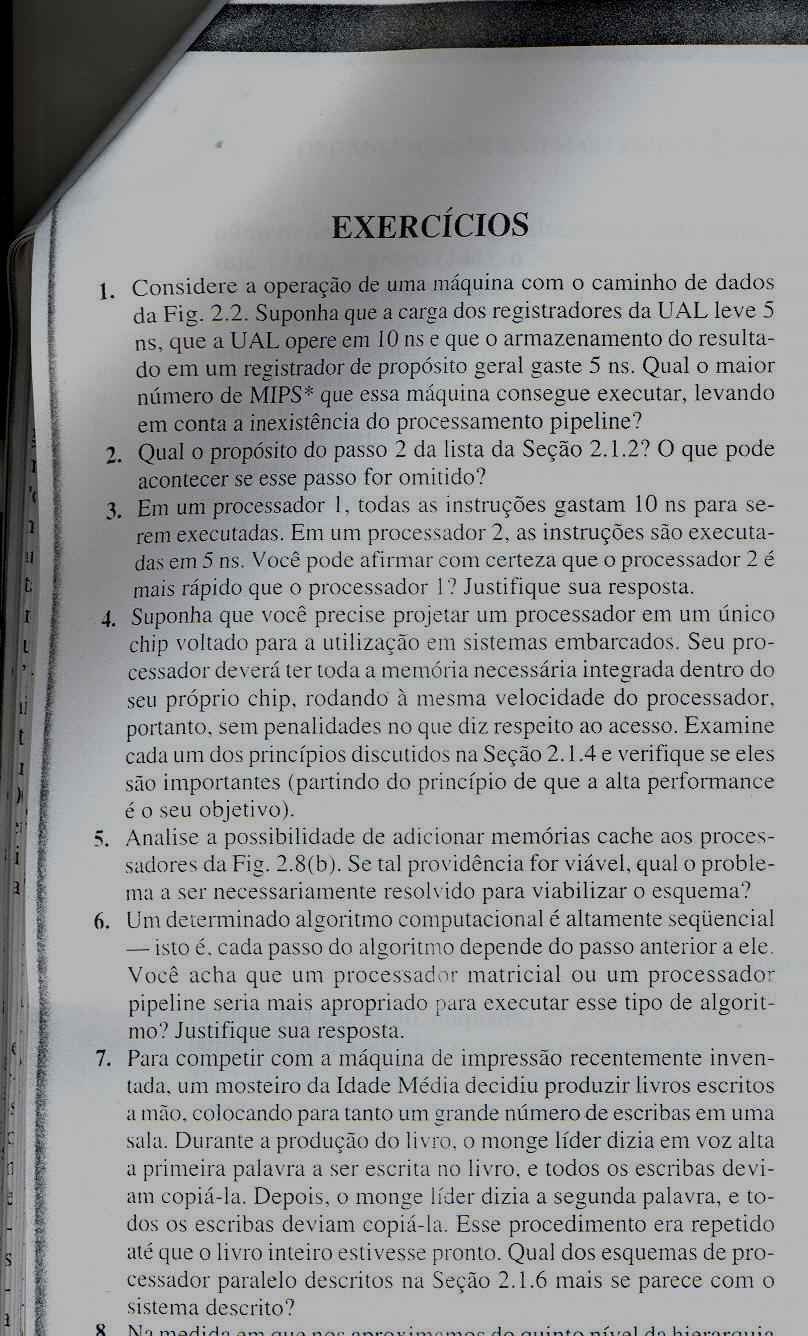

Problemas causados pela falta de padronização

do armazenamento em memória:

- interpretação de instruções e dados

em redes

- softwares que rodam em várias plataformas devem tratar essas

diferenças (swapp de memoria)

- uso de plataformas de palavras de diferentes tamanhos

Importante: A solução para o problema

acima não é trivial, em geral se baseia em inversão

dos bytes. Isto funciona para valores numéricos mas não para

cadeias de caracteres, como mostra a figura 2.12.

Códigos com correção

de erros

Problema: Dados da

memória podem, ocasionalmente, conter erros causados por oscilação

de tensão, por exemplo.

Solução:

- Dados são armazenados na memória com um código

que permita a detecção ou correção

de erros

- São acrescentados bits extras nas palavras de memória

usados para verificar a exatidão da informação

- Uma palavra de código de n (=m+r)

bits conterá: m bits de dados + r bits de redundância

( ou verificação)

Definição:

Distância de Hamming

é igual ao número de bits correspondentes que diferem em duas

palavras de código quaisquer.

As propriedades de detecção

de erros e de correção de erros dependem fundamentalmente

da sua distância de Hamming

Para detectar d erros é

necessário uma distância de hamming igual a d+1, pois

em tal código não há como a ocorrência de d erros

transformar uma palavra de código válida em outra palavra

de código válida.

Para corrigir d erros é

necessário uma distância de hamming igual a 2d+1.

Exemplo: As palavras de código

10001001 e 10110001 tem distância de Hamming igual a 3 (Veja

bits em negrito)

Observação: É

necessário que ocorram 3 erros (inversões) nos bits em negrito

da palavra 2 para que ela se transforme na palavra 1.

Definição:

Bit de Paridade: Definido pelo número

de 1s que ocorrem em uma palavra. Paridade par está associada a um

numero par de 1s e paridade impar está associada a um número

impar de 1s

Exemplo Simples:

- Inclusão de 1 bit de paridade (0 - par e 1 - impar)

aos bits de dados da palavra de código.

- Distância de hamming = 2 portanto a ocorrência de 1 único

erro produz palavra de código errada

- Erro só é detectado, e não corrigido. Programa

cancela o processamento para não gerar resultados errados

Tamanho da Palavra

|

Bits de Verificação

|

Tamanho Total

|

Overhead

percentual

|

8

|

4

|

12

|

50

|

16

|

5

|

21

|

31

|

32

|

6

|

38

|

19

|

64

|

7

|

71

|

11

|

128

|

8

|

138

|

6

|

256

|

9

|

265

|

4

|

512

|

10

|

522

|

2

|

Figura 2.13 Número de Bits de verificação

para um código que corrija um único erro

|

Memória Cache

Problemas

- Acesso a memória, leitura e escrita, é um dos motivos

para menor velocidade de processamento

- Processador é muito mais rápido que a transferência

de dados

Soluções

- Processador deve executar outras instruções enquanto

aguarda acesso a memória. Porém isto nem sempre é possível

e é difícil de implementar.

- Colocar memória principal no Chip do processador. Isto tornaria

o chip maior e mais caro.

- Uso de uma memória menor e mais rápida (em relação

à memória principal) chamada Memória Cache

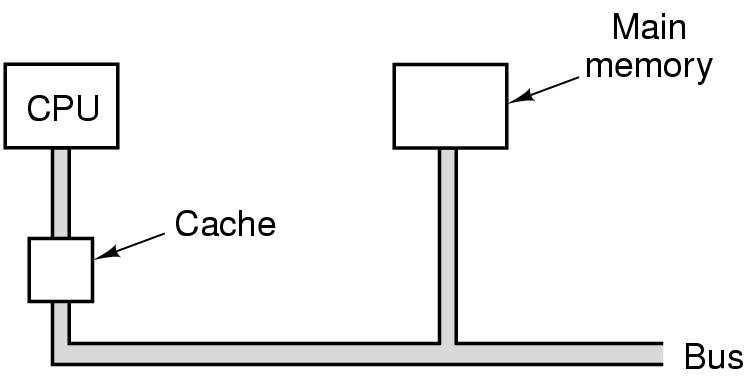

Figura 2.16 Em termos lógicos, a cache é colocada entre o

processador e a memória principal. Em termos físicos, existem

vários lugares possíveis de ela ser colocada

Idéias básicas por trás do conceito

de Memória Cache:

- As palavras de memória mais usadas pelo processador devem

permanecer armazenadas na cache.

- Somente no caso de ela não estar armazenada na cache é

que a busca se dará na memória principal

- Se número de acessos a cache é grande, tempo médio

de acesso à memória diminui significativamente

- Sucesso do esquema depende da fração de acessos satisfeitos

pela cache

- Algumas constatações: uso + frequente de dados recém

usados, de dados de loops e de dados matriciais

- Princípio da localidade: existe uma probabilidade alta

de que as palavras vizinhas de uma palavra recém acessada sejam usadas

em breve. Assim acessa-se a palavra e suas vizinhas, em blocos chamados

linhas da cache, deixando-as armazenadas na cache por um período.

- Podem existir cache só para instruções e só

para dados - arquitetura de Harvard.

- Podem existir caches primárias (dentro do processador) e outra

secundária (fora do chip do processador) e até uma terceira

cache mais externa.

Exercícios capítulo 2