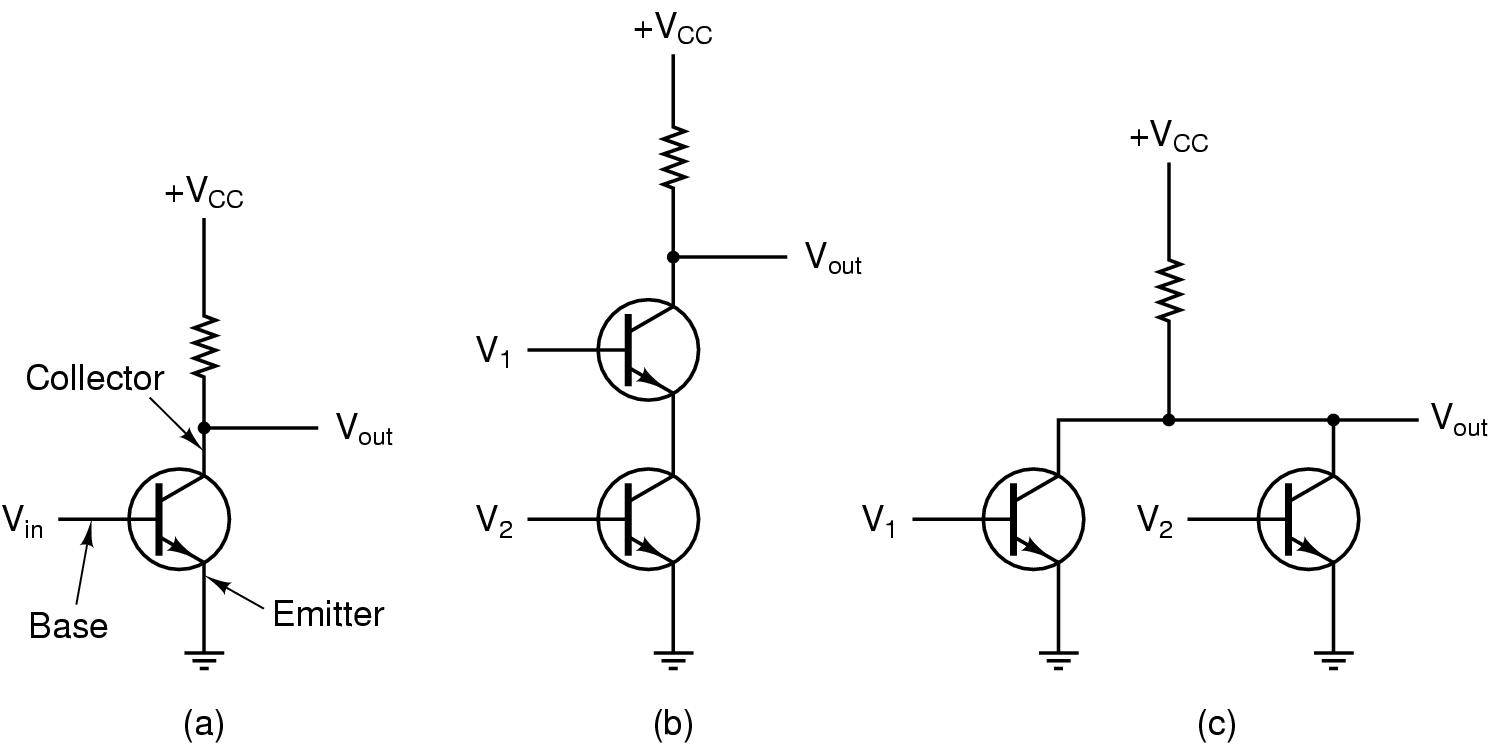

Fig 3.1 (a) Transistor funcionando como inversor. (b) Uma porta NAND. (c) Uma porta NOR

Fig 3.2 Os símbolos e o comportamento funcional de cada uma das 5 portas lógicas básicas

Álgebra Booleana

Fig 3.3 (a) Tabela -verdade para a função maioria de três variáveis. (b) Circuito para a função descrita em (a).

Fig 3.4 Construção de (a) uma porta NOT, (b) uma porta AND e (c) uma porta OR, usando somente portas lógicas NAND ou somente portas lógicas NOR

Equivalência de Circuitos

Fig 3.5 Duas funções equivalentes . (a) AB + AC. (b) A(B + C)

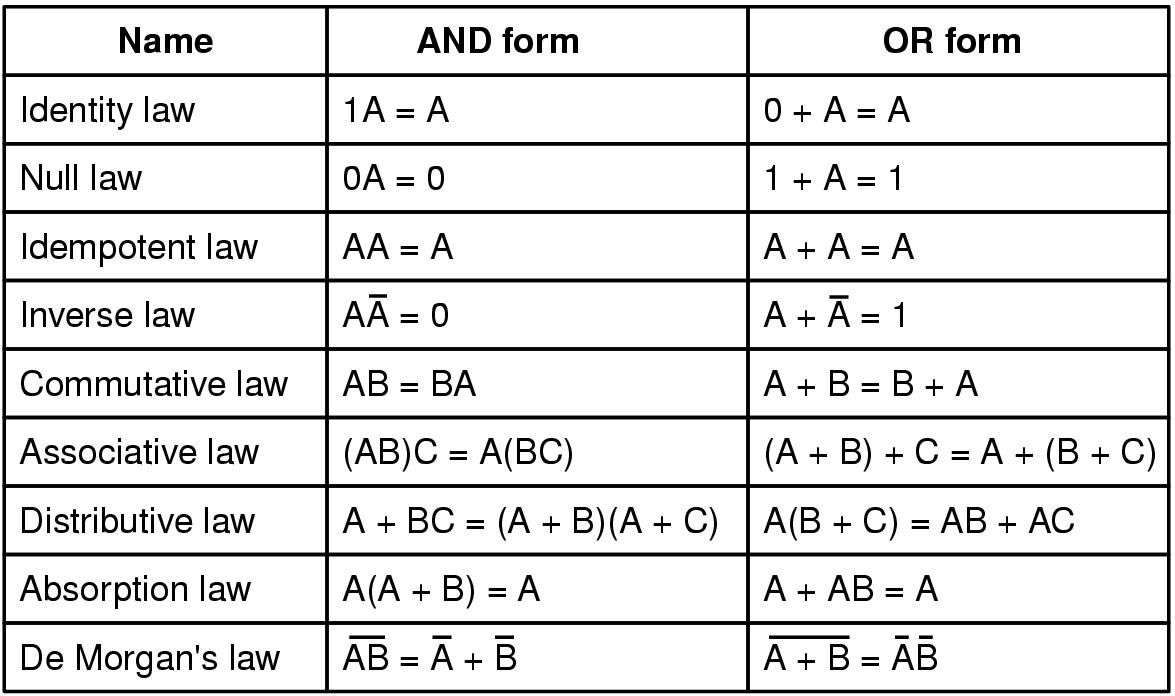

Fig 3.6 Algumas identidades da álgebra de Boole

Fig 3.7 Símbolos alternativos para algumas portas lógicas : (a) NAND (b) NOR (c) AND (d) OR.

Fig 3.8 (a) Tabela verdade para a função XOR. (b) a (d) Três circuitos para calcular a função XOR

Fig 3.9 (a) Características elétricas de um dispositivo. (b) Lógica positiva. (c) Lógica negativa

Fig 3.10- Chip SSI com 4 portas NAND

Fig 3.11 Circuito Multiplexador com 8 entradas

Fig 3.12 (a) Multiplexador MSI. (b) O mesmo multiplexador configurado para calcular a função maioria

Figura 3.13 Circuito Decodificador 3x8

Figura 3.14 Comparador de 4 bits

Figura 3.15 - Matriz lógica programável de 12 entradas e 6 saídas. Os pequenos quadrados que aparecem na figura representam os fusíveis que devem ser queimados para determinar a função a ser calculada. Os fusíveis estão organizados em 2 matrizes: a de cima, composta de portas AND, e a de baixo, composta de portas OR.

Fig 3.16 - Deslocador de 1 bit para a esquerda/direita

Fig 3.17 (a) Tabela-verdade para a soma de 1 bit. (b) Circuito para o meio-somador

Figura 3.18 (a) Tabela verdade e (b) Circuito para o somador completo

Fig 3.19 UAL de 1 bit

Fig 3.20 Oito UALs de 1 bit, conectadas para formar uma UAL de 8 bits. Nao estão mostrados os sinais de inversão e de habilitação.

Fig 3.21 (a) Geração do sinal de clock. (b) O diagrama de tempo para o clock. (c) Geração de um sinal de clock assimétrico.

Fig 3.22 (a) Latch no estado 0 formado por portas NOR. (b) Latch no estado 1 formado por portas NOR. (c) Tabela verdade para a função NOR.

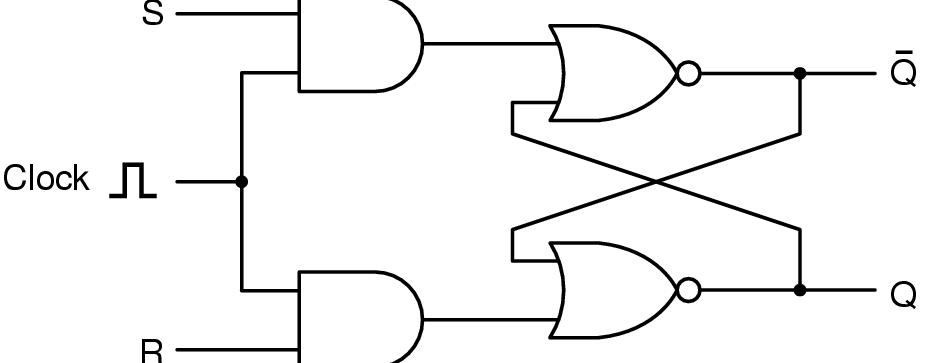

Fig 3.23 Latch SR com clock

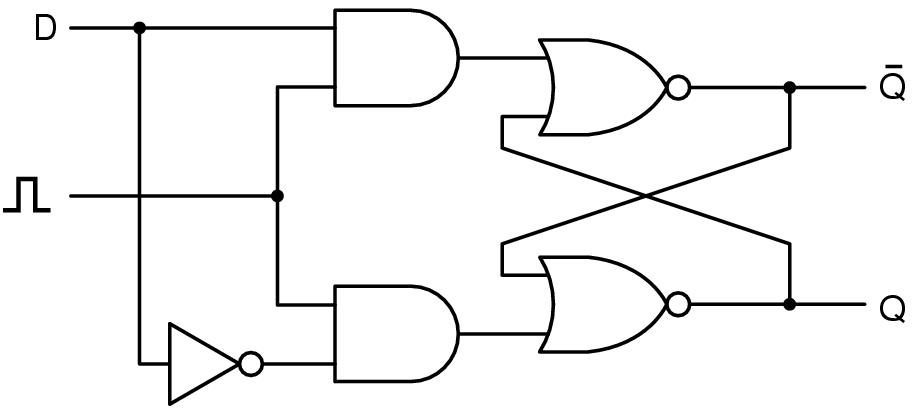

Fig 3.24 Latch D com clock

Fig 3.25 (a) Gerador de Pulsos (b) Temporização em quatro pontos do circuito.

Fig 3.26 Flip-flop D

Fig 3.27 Dois tipos de latches D e dois tipos de flip-flops

Fig 3.28 (a) Chip com dois flip-flops independentes (b) Chip com oito flip-flops

Fig 3.29 Diagrama lógico de uma memória 4x3. Cada linha da memória representa uma palavra de 3 bits. Uma operação de leitura ou de escrita abrange uma palavra

Fig 3.30 (a) Buffer não inversor. (b) Efeito do buffer não inversor quando o sinal de controle está no nível alto. (c) Efeito do buffer não inversor quando o sinal de controle está no nível baixo. (d) Buffer inversor.

Fig 3.31 Duas maneira diferentes de se organizar um chip de memória de 4 Mbit

Fig 3.32 Comparação entre vários tipos de memória