Fig 3.33 Pinagem lógica de um processador genérico. As setas indicam os sinais de entrada e os sinais de saída. As pequenas linhas na diagonal indicam que esse sinal usa vários pinos. No caso de um processador real, em cima da linha diagonal aparece um número para indicar quantos são os pinos usadosUm chip processador

O processador:

A memória:

- Coloca endereço da memória nos pinos de endereço

- Envia sinal de leitura, pino de controle, para a memória

O processador:

- Coloca dados (instrução) da palavra selecionada nos pinos de dados

- Envia sinal de sucesso de leitura, pino de controle, para o processador

- Lê instrução está já está disponível nos pinos de dados

- Inicia execução da instrução

Fig 3.34- Sistema de computador com diversos barramentos

- é um conjunto de regras que especificam o funcionamento do barramento

- define as regras e especificações, elétricas e mecânicas, de compatibilização de 1 conjunto de dispositivos de E/S, em geral fornecidos por terceiros, com o barramento

- mestres: dispositivos ativos, ou seja, que comandam o barramento

- escravos: dispositivos passivos, ou seja, não controlam o barramento

Mestre Escravo

Exemplo

Processador

Memória

Busca de instruções e de dados

Processador

Dispositivos de E/S

Início de transferência de dados

Processador

Co-processador

Envio de instruções do processador para o co-processador

E/S

Memória

DMA (acesso direto à memória)

Co-processador

Processador

Co-processador busca operandos no processador

Fig 3.35 Exemplo de funcionamento de dispositivos como mestres e escravos de barramento

Importante: O barramento tem linhas de endereços, dados e controle, porém não é necessário o mapeamento 1 para 1 com os pinos do processador. Para compatibilizar sinais e pinos dos processadores são usados chips conhecidos como decodificador de barramento.

- alimentador (driver) do barramento: liga mestres de barramento com o barramento

- receptor do barramento: liga escravos de barramento com o barramento

- transceptores do barramento: combinam funcões de alimentador e de receptor para dispositivos que funcionam como mestres e escravos

Fig 3.36 Crescimento do barramento de endereços ao longo do tempoLinhas de dados no barramento:

Barramento Síncronos

A figura abaixo mostra um exemplo de leitura de dado pelo processador que segue os seguintes passos:

- Funcionam com um clock (oscilador de cristal, de 5 a > 100MHz)

- Todas atividades gastam pelo m ciclos inteiros de ciclos de barramento

- O processador coloca endereço de memória no barramento, depois da subida de T1 (T1+retardo Tad)

- Ativa MREQ' (leia MREQ barrado) e RD' na descida de T1 (T1 + retardos)

- A memória ativa WAIT' na subida de T2 para informar que está trabalhando

- A memória desativa WAIT' na subida de T3 para dizer que dados estão disponíveis

- O processador lê dados, depois da subida de T3 (com retardo Tds)

- O processador avisa que leu os dados (MREQ' =1 e RD' = 1) depois da descida de T3+retardo

Fig 3.37 (a) Temporização para uma operação de leitura usando um barramento síncrono (b) Especificação de alguns tempos críticos

Importante: O maior problema com os barramento síncronos é que os dispositivos mais rápidos tem que esperar alguns clocks inteiros para finalização de operações com dispositivos mais lentos

Barramento Assíncronos

Exemplo de funcionamento de um barramento assíncrono

- Não usam clock mestre para sincronização de operações

Obs: Os dois parágrafos abaixo foram copiados totalmente do livro texto.

A figura 3.38 mostra o diagrama de tempo de um barramento assíncrono. Em vez de amarrar todos os eventos ao clock, quando o mestre do barramento ativar o endereço, os sinais MREQ' e RD' e tudo mais que for necessário, um sinal especial, conhecido como MSYN' (Master SYNchronization), deve ser ativado. Quando enxerga o MSYN' ativo, o escravo faz seu trabalho o mais rápido que puder. Ao terminar, ele ativa o sinal SSYN' (Slave SYNchronization).

O sinal SSYN' ativo informa ao mestre que os dados estão disponíveis, fazendo com que o mestre armazene os dados e então negue as linhasde endereçoi, junto com MREQ', RD' e MSYN'. Ao enxergar a negação de MSYN' , o escravo sabe que o ciclo terminou, de modo que ele nega SSYN' , levando o processo de volta à situação original, em que todos os sinais negados aguardam o próximo mestre.

Fig 3.38 Operação de um barramento assíncronoO barramento assíncrono tem vantagens em relação ao síncrono, porém os síncronos são mais usados pois:

- são mais fáceis de construir, não precisam de sinais de sincronização dos mestres e escravos

- há uma boa soma de dinheiro investida na tecnologia de barramentos síncronos

Questão: O que acontece se dois ou mais dispositivos desejarem tornar-se mestres do barramento ao mesmo tempo?

Solução: Estabelece-se um mecanismo para efetuar a arbitragem do barramento que podem ser mecanismos centralizados ou não centralizados.

Arbitragem descentralizada

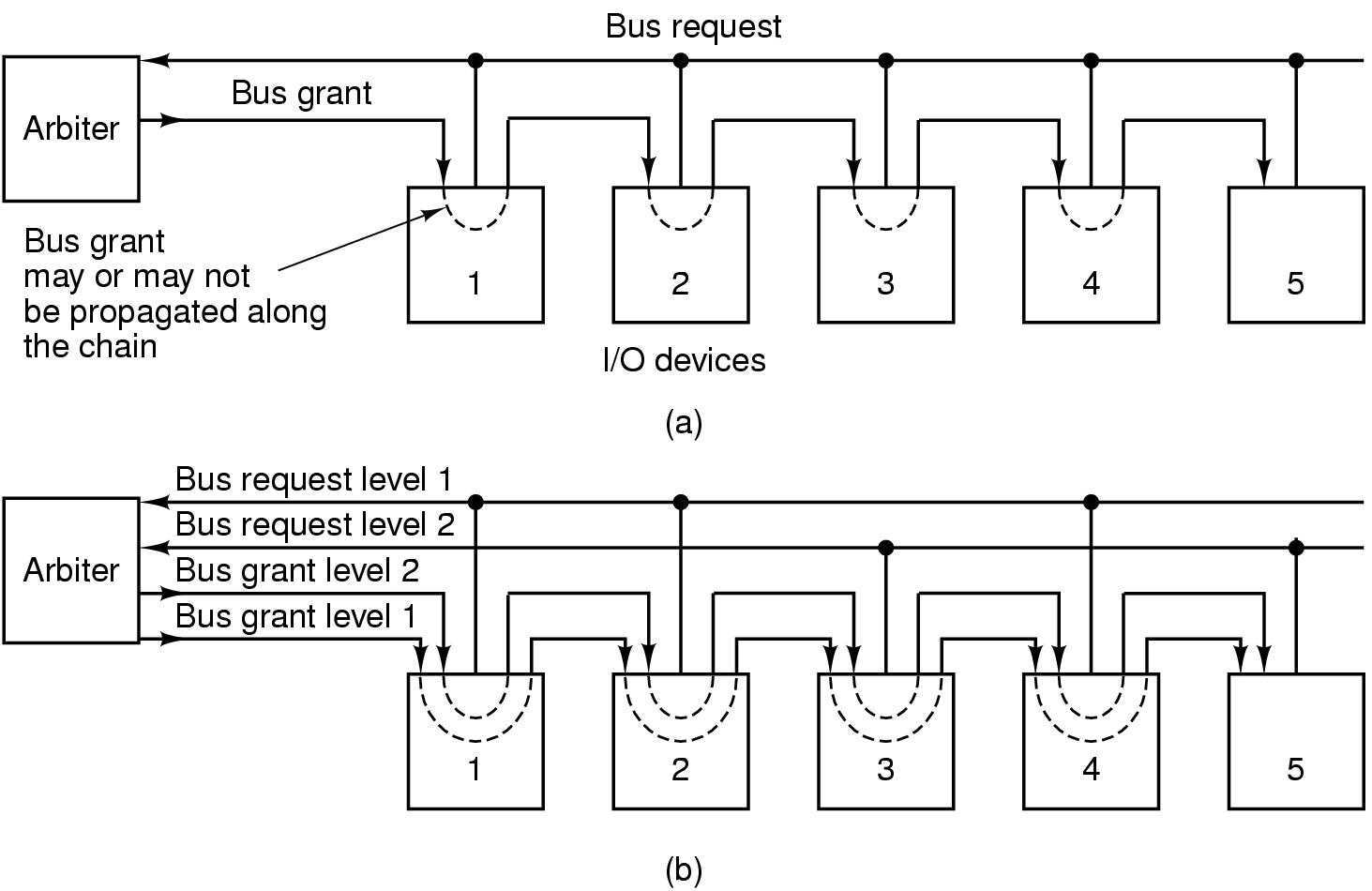

Bus request level n - requisição de uso do barramento de nível n

Bus grant level n - garantia de uso do barramento de nível n

Figura 3.39 (a) Árbitro centralizado operando com um nível, usando arbitragem daisy chain. (b) O mesmo árbitro operando com 2 níveis

Figura 3.40 Arbitragem descentralizada do barramento

Figura 3.41 Transferência de um bloco

a. Um hambúrguer2. Um missionário perdido no sul da Califómia pára em uma encruzilhada da estrada. Ele sabe que o local é freqüentado por duas gangues de motoqueiros, e sabe também que os membros de uma delas sempre dizem a verdade e os membros da outra sempre mentem. Ele deseja saber qual das duas estradas leva à Disneylândia. Qual pergunta ele deve fazer ao membro da gangue que aparecer na estrada de maneira a ter certeza de que a informação dada é correta?

b. Um cachorro-quente.

c. Batatas fritas.

d. Um cachorro-quente e batatas fritas.

e. Um hambúrguer e batatas fritas.

f. Um cachorro-quente e um hambúrguer.

g. Um hambúrguer, um cachorro-quente e batatas fritas.

h. Nada.