Fig 4.1 O caminho de dados da microarquitetura usada neste capítuloO caminho de dados contém:

A função a ser executada pela UAL é determinada pelas 6 linhas de controle

- F0 e F1 para determinação da operação

- ENA e ENB para habilitar individualmente suas entradas A e B

- INVA para inverter a entrada de A

- INC que força um vem-um para o bit menos significativo (incremento de 1)

- A figura 4.2 apresenta algumas combinações úteis desses sinais de contrôle

Observações:

Fo F1 ENA ENB INVA INC Função O 1 1 O O O A O 1 O 1 O O B O 1 1 O 1 O A' (A negado) 1 O 1 1 O O B' (B negado) 1 1 1 1 O O A+B 1 1 1 1 O 1 A+B+1 1 1 1 O O 1 A+1 1 1 O 1 O 1 B+1 1 1 1 1 1 1 B-A 1 1 O 1 1 O B-1 1 1 1 O 1 1 -A O O 1 1 O O A AND B O 1 1 1 O O A OR B O 1 O O O O O O 1 O O O 1 1 O 1 O O 1 0 -1

Fig. 4.2 Combinações úteis dos sinais de controle da UAL com as funções executadas por cada uma delas.

- O registrador H pode ser carregado com o valor presente no barramento B, realizando-se uma soma com o sinal ENA desabilitado (ENA=0).

- Deslocamentos a direita e à esquerda podem ser comandados pelos sinais de controle do deslocador. Exemplos:

- SLL8 - desloca a saída da UAL 1 byte a esquerda, deixando 0s no byte da direita

- SRR1 - deslocamento a saída da UAL 1 bit para a direita, sem modificar o bit + significativo (bit de sinal)

Temporização do caminho de dados

Questão:

Um registrador pode ser lido e escrito no mesmo ciclo de clock sem produzir lixo?

Resposta:

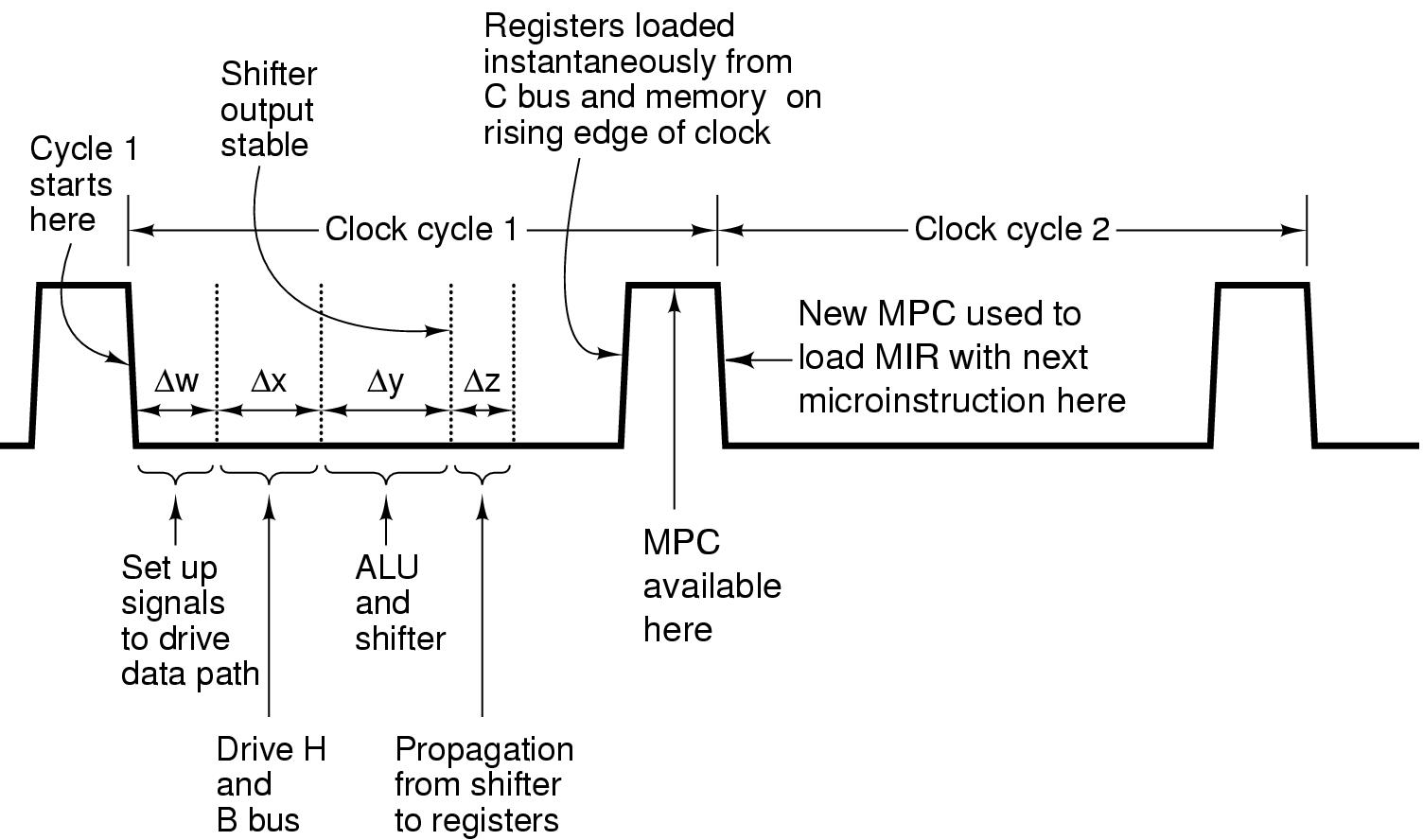

A temporização exata do caminho de dados torna possível a leitura e a escrita de um registrador no mesmo período de clock. Como isto é feito está mostrado na Figura 4.3

Fig 4.3 Diagrama de tempo de um dos ciclos do caminho de dados.

Fig 4.3 Diagrama de tempo de um dos ciclos do caminho de dados.

- O primeiro ciclo (explicito, do caminho de dados, apresentado na figura 4.3, pode ser visto como um conjunto de subciclos implícitos

- O início do primeiro subciclo é marcado pela transição negativa do clock.

- As atividades, junto com sua duração (entre parênteses), que ocorrem durante os subciclos são:

- Os sinais de controle são ativados (dw - leia delta w)

- O barramento B é carregado a partir dos registradores (dx)

- A UAL e o deslocador operam (dy)

- O resultado da operação da UAL e do deslocador se propaga através do barramento C em direção aos registradores (dz)

- O resultado é armazenado nos registradores na transição positiva do próximo clock

- É de responsabilidade dos engenheiros de projeto assegurar que essa transição positiva ocorra somente após passado o tempo dw+dx+dy+dz. Caso contrário a carga dos registradores não é realizada

Operação da Memória

- Nossa máquina se comunica com a memória:

- por uma porta de memória de 32 bits que é controlada por 2 registradores:

- o MAR (Memory Address Register), registrador de endereços

- o MDR (Memory Data Register), registrador de dados

- e por uma porta de memória de 8 bits que é controlada por um terceiro registrador, conhecido como PC. O PC lê um byte da memória e coloca-o nos 8 bits menos significativos de um registrador conhecido como MBR (Memory Buffer Register)

- A combinação MAR/MDR é usada para ler/escrever palavras de dados pertencentes ao nível ISA

- A combinação PC/MBR é usada para ler o programa executável, grupo de bytes, do nível ISA

- Cada um dos registradores é controlado por um ou dois sinais de controle, situados em baixo do registrador:

- uma seta clara indicando que o sinal de controle habilita a saída do registrador para o barramento B.

- uma seta escura indicando que o sinal de controle habilita a carga do registrador a partir do barramento C.

- A figura 4.4 mostra que os dois bits mais significativos são descartados no mapeamento do seu conteúdo para o barramento de endereços (por exemplo, valor 1 vira 4). Tais bits só são necessários para endereçar palavras acima de 232, o que não é permitido na nossa máquina de 4GB.

Fig 4.4 Mapeamento dos bits do MAR nos bits do barramento de endereço

- O conteúdo do registrador MBR pode ser copiado no barramento B de duas formas:

- como um valor sem sinal: neste caso o byte do MBR é copiado no byte menos significativo de B e os demais bits desse barramento conterão 0s

- como um valor com sinal: neste caso o byte do MBR é copiado no byte menos significativo de B e terá o seu bit mais significativo (bit de sinal) copiado para os demais bits desse barramento (processo conhecido como extensão de sinal).

Para controlar um caminho de dados, como o da figura 4.1, precisamos de um conjunto de sinais de controle que atuam sobre os componentes do nível da lógica digital.

Os valores desses sinais de controle especificam as operações a serem executadas em um ciclo do caminho de dados.

A figura 4.5 mostra um possível formato para agrupar os bits de controle da nossa arquitetura em 6 grupos, e 36 sinais, assim divididos:

- Endereço - contém o endereço da próxima instrução a ser potencialmente ativada

- Desvio - determina como a próxima instrução será selecionada

- UAL - especifica as funções da UAL e do deslocador

- Barramento C - seleciona qual ou quais registradores serão carregados com o valor que estiver no barramento C

- Memória - especifica as funções da memória (escrita, leitura ou busca)

- Barramento B - seleciona a entrada do barramento B. Os 4 bits são suficientes para selecionar um dos 9 registradores que disponibilizará seus dados no barramento B.

Fig 4.5 Formato da microinstrução do Mic-1

Para decidir quais dos sinais de controle devem ser habilitados em cada ciclo faz-se necessário a inclusão de um sequenciador em nossa arquitetura.

O sequenciador:

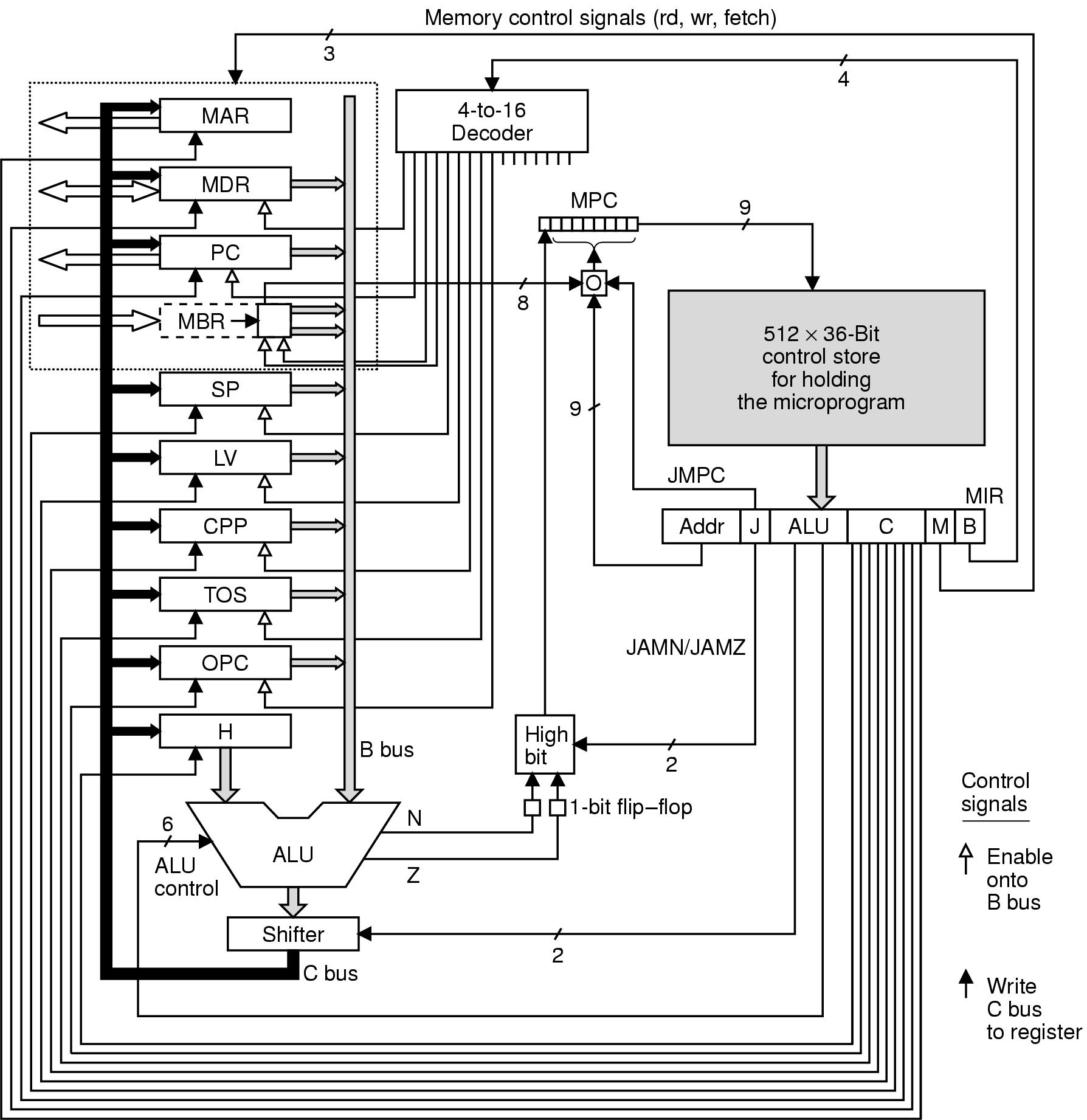

A figura 4.6 mostra o diagrama de blocos detalhado da microarquitetura de nossa máquina-exemplo, que receberá o nome de Mic-1.

- é responsável pela execução de todos os passos necessários a execução de 1 única instrução do nível ISA.

- produz dois tipos de informações a cada ciclo:

- 1. O estado de cada sinal de controle do sistema

- 2. O endereço da microinstrução que será executada em seguida

O diagrama de blocos tem 2 partes: O caminho de dados, à esquerda e a seção de controle, à direita.

A memória de controle:

As microinstruções não são executadas sequencialmente, como as instruções da memória principal. Cada microinstrução especifica explicitamente sua sucessora.

- É o ítem maior e mais importante da parte de controle da máquina

- Não deve ser confundida com a memória principal (RAM), acessível via MBR e MDR

- Não precisa de sinais de leitura/escrita pois é uma memória ROM (só de leitura)

- Guarda microinstruções, ao invés de instruções do nível ISA

- Tem 512 palavras, cada palavra contendo uma instrução de 36 bits, do tipo da figura 4.5

O endereço da próxima microinstrução é guardado no registrador MPC (Microprogram Counter)

O registrador de dados da memória de controle é chamado MIR (MicroInstruction Register). Sua função é armazenar a microinstrução corrente cujos bits alimentam os sinais de controle que operam o caminho de dados.

Fig 4.6 Diagrama de blocos completo do Mic-1, a máquina cuja microarquitetura é utilizada em nosso exemplo.

Operação do esquema mostrado na figura 4.6

A atualização do MPC é feita por:

- No início de cada ciclo (na descida do clock da fig 4.3) o MIR é carregado com o conteúdo do endereço armazenado no MPC. O tempo de carga do MIR é dw (leia delta w)

- Os sinais do MIR se propagam pelo caminho de dados, causando, no tempo dx:

- o carregamento de 1 dos registradores no barramento B

- o carregamento do registrador H

- a determinação da função a ser executada pela UAL

- estabilização dos dados de entrada da UAL

- A UAL e o deslocador operam os dados de entrada, durante o tempo dy:

- As saídas da UAL e do deslocador são propagadas, durante o tempo dz, e

- a saída do deslocador torna-se disponível e estável no barramento C

- os valores de N e Z são salvos em 1 par de flip-flops de 1 bit

- Na transição positiva do sinal de clock, da figura 4.3.

- os registradores são carregados com o conteúdo do barramento C

- os flip-flops N e Z são carregados pela UAL

- os registradores MBR e MDR recebem resultados da memória

- O valor de MPC é atualizado (veja detalhes abaixo) no tempo de nível alto do clock.

- Volta ao passo 1 e o ciclo se repete até que alguem desligue a máquina.

F=(JAMZ AND Z) OR (JAMN AND N) OR NEXT_ADDRESS[8]

- um circuito lógico, chamado bit de mais alta ordem, que implementa a função:

Assim os dois únicos valores que o MPC pode assumir são:

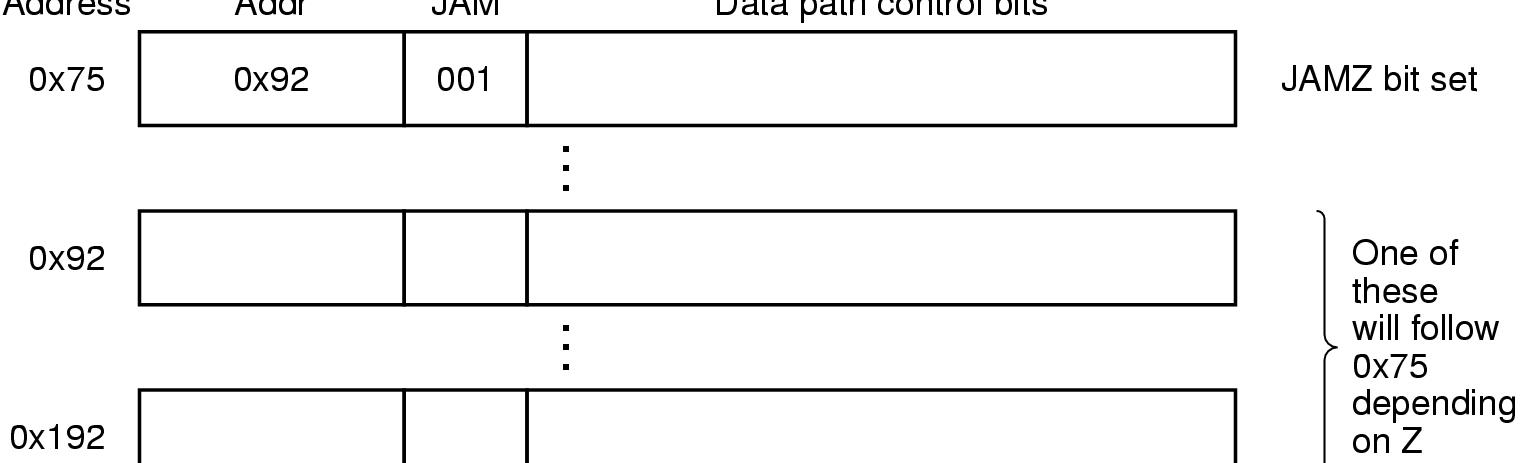

Observação: O valor do campo NEXT_ADDRESS não mudará se JAMZ= JAMN=0. A figura 4.7 ilustra essa operação quando o bit JAMZ está ligado (=1)

- O valor do campo NEXT_ADDRESS

- O valor do campo NEXT_ADDRESS com o bit de mais alta ordem submetido à operação OR com o valor 1.

- uma circuito lógico, caixa O da figura 4.6. Se o sinal de desvio é igual a 1, esse circuito implementa uma função OR bit a bit entre o MBR (que em geral contém um código de operação) e os 8 bits menos significativos do NEXT_ADDRESS corrente.